## (De/Re)-Composition of Data-Parallel Computations via Multi-Dimensional Homomorphisms

ARI RASCH, University of Muenster, Germany

Data-parallel computations, such as linear algebra routines and stencil computations, constitute one of the most relevant classes in parallel computing, e.g., due to their importance for deep learning. Efficiently de-composing such computations for the memory and core hierarchies of modern architectures and re-composing the computed intermediate results back to the final result—we say (*de/re)-composition* for short—is key to achieve high performance for these computations on, e.g., GPU and CPU. Current high-level approaches to generating data-parallel code are often restricted to a particular subclass of data-parallel computations and architectures (e.g., only linear algebra routines on only GPU or only stencil computations), and/or the approaches rely on a user-guided optimization process for a well-performing (de/re)-composition of computations, which is complex and error prone for the user.

We formally introduce a systematic (de/re)-composition approach, based on the algebraic formalism of Multi-Dimensional Homomorphisms (MDHs). Our approach is designed as general enough to be applicable to a wide range of data-parallel computations and for various kinds of target parallel architectures. To efficiently target the deep and complex memory and core hierarchies of contemporary architectures, we exploit our introduced (de/re)-composition approach for a correct-by-construction, parametrized cache blocking, and parallelization strategy. We show that our approach is powerful enough to express, in the same formalism, the (de/re)-composition strategies of different classes of state-of-the-art approaches (scheduling-based, polyhedral, etc.), and we demonstrate that the parameters of our strategies enable systematically generating code that can be fully automatically optimized (auto-tuned) for the particular target architecture and characteristics of the input and output data (e.g., their sizes and memory layouts). Particularly, our experiments confirm that via auto-tuning, we achieve higher performance than state-of-the-art approaches, including hand-optimized solutions provided by vendors (such as NVIDIA cuBLAS/cuDNN and Intel oneMKL/oneDNN), on real-world datasets and for a variety of data-parallel computations, including linear algebra routines, stencil and quantum chemistry computations, data mining algorithms, and computations that recently gained high attention due to their relevance for deep learning.

# CCS Concepts: • Computing methodologies → Parallel computing methodologies; *Machine learning*; • Theory of computation → Program semantics; • Software and its engineering → Compilers;

Additional Key Words and Phrases: Code generation, data parallelism, auto-tuning, GPU, CPU, OpenMP, CUDA, OpenCL, linear algebra, stencils computation, quantum chemistry, data mining, deep learning

© 2024 Copyright held by the owner/author(s). Publication rights licensed to ACM.

https://doi.org/10.1145/3665643

A full version of this article is provided by Rasch [2024], which presents our novel concepts with all of their formal details. In contrast to the full version, this article relies on a simplified formal foundation for better illustration and easier understanding. We often refer the interested reader to Rasch [2024] for formal details that should not be required for understanding the basic ideas and concepts of our approach.

This work was funded by the Deutsche Forschungsgemeinschaft (DFG, German Research Foundation)—project PPP-DL (470527619).

Author's Contact Information: Ari Rasch (Corresponding author), University of Muenster, Muenster, Germany; e-mail: a.rasch@uni-muenster.de.

Permission to make digital or hard copies of all or part of this work for personal or classroom use is granted without fee provided that copies are not made or distributed for profit or commercial advantage and that copies bear this notice and the full citation on the first page. Copyrights for components of this work owned by others than the author(s) must be honored. Abstracting with credit is permitted. To copy otherwise, or republish, to post on servers or to redistribute to lists, requires prior specific permission and/or a fee. Request permissions from permissions@acm.org.

ACM 1558-4593/2024/10-ART10

#### **ACM Reference format:**

Ari Rasch. 2024. (De/Re)-Composition of Data-Parallel Computations via Multi-Dimensional Homomorphisms. *ACM Trans. Program. Lang. Syst.* 46, 3, Article 10 (October 2024), 74 pages. https://doi.org/10.1145/3665643

#### 1 Introduction

Data-parallel computations constitute one of the most relevant classes in parallel computing. Important examples of such computations include linear algebra routines [Whaley and Dongarra, 1998], various kinds of stencil computations (e.g., Jacobi method and convolutions) [Hagedorn et al., 2018], quantum chemistry computations [Kim et al., 2019], and data mining algorithms [Rasch et al., 2019b]. The success of many application areas critically depends on achieving high performance for their data-parallel building blocks, on a variety of parallel architectures. For example, highly optimized linear algebra routines implementations combined with the computational power of modern GPUs currently enable deep learning to significantly outperform other existing machine learning approaches (e.g., for speech recognition and image classification).

Data-parallel computations are characterized by applying the same function (a.k.a *scalar function*) to each point in a multi-dimensional grid of data (a.k.a. *array*) and combining the obtained intermediate results in the grid's different dimensions using so-called *combine operators*.

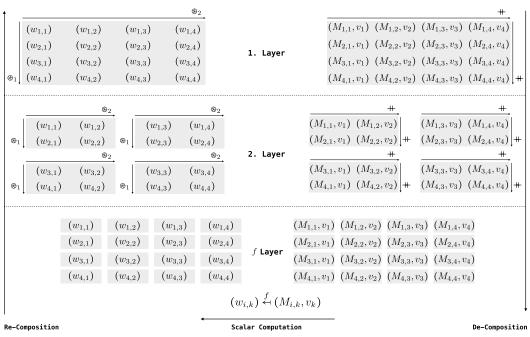

Figures 1 and 2 illustrate data parallelism using as examples two popular computations: (1) linear algebra routine *Matrix-Vector multiplication* (MatVec) and (2) stencil computation *Jacobi* (Jacobi 1D). In the case of MatVec, the grid is two-dimensional and consists of pairs, each pointing to one element of the input matrix  $M_{i,k}$  and the vector  $v_k$ . To each pair, scalar function  $f(M_{i,k}, v_k) := M_{i,k} * v_k$  (multiplication) is applied, and results in the *i*-dimension are combined using combine operator  $\mathfrak{D}_1((x_1, \ldots, x_n), (y_1, \ldots, y_m)) := (x_1 + y_1, \ldots, y_m)$  (concatenation) and in *k*-dimension using operator  $\mathfrak{D}_2((x_1, \ldots, x_n), (y_1, \ldots, y_n)) := (x_1 + y_1, \ldots, x_n + y_n)$  (point-wise addition). Similarly, the scalar function of Jacobi 1D is  $f(v_{i+0}, v_{i+1}, v_{i+2}) := c * (v_{i+0} + v_{i+1} + v_{i+2})$  which computes the Jacobi-specific function for an arbitrary but fixed constant *c*; Jacobi 1D's combine operator  $\mathfrak{D}_1$  is a point of the scalar function. We formally define scalar functions and combine operator so the scalar in this article.

Achieving high performance for data-parallel computations is considered important in both academia and industry but has proven to be challenging. In particular, achieving high performance that is *portable* (i.e., the same program code achieves a consistently high level of performance across different architectures and characteristics of the input/output data, e.g., their size and memory layout) and in a user-productive way is identified as an ongoing, major research challenge. This is because for high performance, an efficient (de/re)-composition of computations (illustrated in Figure 3 and discussed thoroughly in this article) is required to efficiently break down a computation for the deep and complex memory and core hierarchies of state-of-the-art architectures, via efficient cache blocking and parallelization strategies. Moreover, to achieve performance that is portable across architectures, the programmer has to consider that architectures often differ significantly in their characteristics [Sun et al., 2019]-depth of memory and core hierarchies, automatically managed caches (as in CPUs) vs. manually managed caches (as in GPUs), and so on-which poses further challenges on identifying an efficient (de/re)-composition of computations. Productivity is often also hampered: state-of-the-art programming models (such as OpenMP [OpenMP, 2022] for CPU, CUDA [NVIDIA, 2022g] for GPU, and OpenCL [Khronos, 2022b] for multiple kinds of architectures) operate on a low abstraction level; thereby, the models require from the programmer explicitly implementing a well-performing (de/re)-composition, which involves complex and error-prone index computations, explicitly managing memory and threads on multiple layers, and so on.

Current high-level approaches to generating data-parallel code usually struggle with addressing in one combined approach all three challenges: *performance*, *portability*, and *productivity*. For

(De/Re)-Composition of Data-Parallel Computations via MDHs

$$\begin{pmatrix} M_{1,1} & \dots & M_{1,K} \\ \vdots & \ddots & \vdots \\ M_{I,1} & \dots & M_{I,K} \end{pmatrix}, \begin{pmatrix} v_1 \\ \vdots \\ v_K \end{pmatrix} \xrightarrow{\mathsf{f}(M_{1,1},v_1)} \dots & f(M_{I,K},v_K) \\ \stackrel{\mathsf{MatVec}}{\vdots} & \ddots & \vdots \\ f(M_{I,1},v_1) & \dots & f(M_{I,K},v_K) \end{pmatrix} = \begin{pmatrix} M_{1,1} * v_1 + \dots + M_{1,K} * v_K \\ \vdots \\ M_{I,1} * v_1 + \dots + M_{I,K} * v_K \end{pmatrix} = \begin{pmatrix} w_1 \\ \vdots \\ w_I \end{pmatrix}$$

Fig. 1. Data parallelism illustrated using the example Matrix-Vector Multiplication (MatVec).

Fig. 2. Data parallelism illustrated using the example Jacobi 1D (Jacobi1D).

example, approaches such as Halide [Ragan-Kelley et al., 2013], Apache TVM [Chen et al., 2018a], Fireiron [Hagedorn et al., 2020a], and LoopStack [Wasti et al., 2022] achieve high performance but incorporate the user into the optimization process-by requiring from the user explicitly expressing optimizations in a so-called scheduling language-which is error prone and needs expert knowledge about low-level code optimizations, thus hindering user's productivity. In contrast, polyhedral approaches, such as Pluto [Bondhugula et al., 2008b], PPCG [Verdoolaege et al., 2013], and Facebook's TC [Vasilache et al., 2019], are often fully automatic and thus productive but usually specifically designed toward a particular architecture (e.g., only GPU as TC and PPCG, or only CPU as Pluto) and thus not portable. Functional approaches, e.g., Lift [Steuwer et al., 2015], are productive for functional programmers (e.g., with experience in Haskell [Haskell.org, 2022] programming, which relies on small, functional building blocks for expressing computations), but the approaches often have difficulties in automatically achieving the full performance potential of architectures [Rasch et al., 2019a]. Furthermore, many of the existing approaches are specifically designed toward a particular subclass of data-parallel computations only, e.g., only tensor operations (as LoopStack and TC) or only matrix multiplication (as Fireiron), or they require significant extensions for new subclasses (as Lift for matrix multiplication [Remmelg et al., 2016] and stencil computations [Hagedorn et al., 2018]), which further hinders the productivity of the user.

In this article, we formally introduce a systematic (de/re)-composition approach for data-parallel computations targeting state-of-the-art parallel architectures. We express computations via *high-level functional expressions* (specifying *what* to compute), in the form of easy-to-use higher-order functions, based on the algebraic formalism of **Multi-Dimensional Homomorphisms (MDHs**)<sup>1</sup> [Rasch and Gorlatch, 2016].<sup>2</sup> Our higher-order functions are capable of expressing various kinds of data-parallel computations (linear algebra, stencils, etc.), in the same formalism and on a high level of abstraction, independently of hardware and optimization details, thereby contributing to user's productivity.<sup>3</sup> As target for our high-level expressions, we introduce *functional low-level expressions* (specifying *how* to compute) to formally reason about (de/re)-compositions of data-parallel computations; our low-level expressions are designed such that they can be straightforwardly transformed to executable program code (e.g., in OpenMP, CUDA, and OpenCL). To systematically lower our high-level expressions to low-level expressions, we introduce a formally sound, parameterized *lowering process*. The parameters of our lowering process enable automatically computing low-level expressions that are optimized (auto-tuned [Balaprakash et al., 2018]) for the particular target architecture and characteristics of the input/output data, thereby achieving fully automatically

<sup>1</sup>https://mdh-lang.org

<sup>2</sup>We thoroughly compare to the existing MDH work in Section 6.6.

<sup>3</sup>We consider as main users of our approach compiler engineers and library designers. Rasch et al. [2020b] show that our approach can also take straightforward, sequential code as input, which makes our approach attractive also to end users.

Fig. 3. Example (de/re)-composition of MatVec (Figure 1) on a  $4 \times 4$  input matrix M and a 4-sized vector v: (1) the *de-composition phase* (right part of the figure) partitions the concatenated input data into parts (a.k.a. tiles in programming), where # denotes the concatenation operator; (2) to each part, scalar function f is applied in the *scalar phase* (bottom part of figure), which is defined for MatVec as multiplying matrix element  $M_{i,k}$  with vector element  $v_k$ , resulting in element  $w_{i,k}$ ; (3) the *re-composition phase* (figure's left part) combines the computed parts to the final result, using combine operator  $\otimes_1$  for the first dimension (defined as concatenation in the case of MatVec) and operator  $\otimes_2$  (point-wise addition) for the second dimension. All basic building blocks (scalar function, combine operator, ...) and concepts (e.g., partitioning) are defined in this article, based on algebraic concepts. For simplicity, this example presents a (de/re)-composition on two layers only, and we partition the input for this example into parts that have straightforward, equal sizes. Optimized values of semantics-preserving parameters (a.k.a. tuning parameters), such as the number of parts and the application order of combine operators, are crucial for achieving high performance, as we discuss in this article. Phases are arranged from right to left, inspired by the application order of function composition, as we also discuss later.

high, portable performance. For example, we formally introduce parameters for flexibly choosing the target memory regions for de-composed and re-composed computations and also parameters for flexibly setting an optimized data access pattern.

We show that our high-level representation is capable of expressing various kinds of dataparallel computations, including computations that recently gained high attention due to their relevance for deep learning [Barham and Isard, 2019]. For our low-level representation, we show that it can express the cache blocking and parallelization strategies of state-of-the-art parallel implementations-as generated by scheduling approach TVM and polyhedral compilers PPCG and Pluto-in one uniform formalism. Moreover, we present experimental results to confirm that based on our parameterized lowering process in combination with auto-tuning, we are able to achieve higher performance than the state of the art, including hand-optimized implementations provided by vendors (e.g., NVIDIA cuBLAS and Intel oneMKL for linear algebra routines, and NVIDIA cuDNN and Intel oneDNN for deep learning computations).

10:4

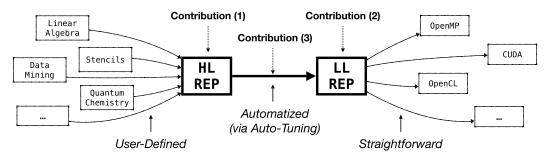

Fig. 4. Overall structure of our approach (contributions highlighted in bold).

Summarized, we make the following three major contributions (illustrated in Figure 4):

- (1) We introduce a functional **High-Level Representation (HL REP)**, based on the algebraic formalism of MDHs, that enables uniformly expressing data-parallel computations on a high level of abstraction.

- (2) We introduce a functional Low-Level representation (LL REP) that enables formally expressing and reasoning about (de/re)-compositions of data-parallel computations; our low-level representation is designed such that it can be straightforwardly transformed to executable program code in state-of-practice parallel programming models, including OpenMP, CUDA, and OpenCL.

- (3) We introduce a *systematic lowering process* to fully automatically lower an expression in our high-level representation to a device- and data-optimized expression in our low-level representation, in a formally sound manner, based on auto-tuning.

Our three contributions aim to answer the following questions:

- How can data parallelism be formally defined, and how can data-parallel computations be uniformly expressed via higher-order functions that are agonistic from hardware and optimization details while still capturing all information relevant for generating high-performing, executable program code? (Contribution 1)

- (2) How can optimizations for the memory and core hierarchies of state-of-the-art parallel architectures be formally expressed and generalized such that they apply to arbitrary data-parallel computations? (Contribution 2)

- (3) How can optimizations for data-parallel computations be expressed and structured so that they can be automatically identified (auto-tuned) for a particular target architecture and characteristics of the input and output data? (Contribution 3)

The rest of the article is structured as follows. We introduce our functional HL REP (Contribution 1) in Section 2, and we show how this representation is used for expressing various kinds of popular data-parallel computations. In Section 3, we discuss our functional LL REP (Contribution 2) which is powerful enough to express the optimization decisions of state-of-practice approaches (e.g., scheduling approach TVM and polyhedral compilers PPCG and Pluto) and beyond. Section 4 shows how we systematically lower a computation expressed in our high-level representation to an expression in our low-level representation, in a formally sound and auto-tunable manner (Contribution 3). We present experimental results in Section 5, discuss related work in Section 6, conclude in Section 7, and we present our ideas for future work in Section 8.

We provide a full version of this paper [Rasch, 2024] that contains details for the interested reader that should not be required for understanding the basic concepts introduced in this article.

Fig. 5. High-level representation (overview).

In particular, our full version contains formal details—for all the following definition, examples, and theorems in Sections 2–4—whereas the formalism in this article is simplified for better illustration and easier understanding of our basic ideas and concepts.

#### 2 High-Level Representation for Data-Parallel Computations

We introduce functional building blocks, in the form of higher-order functions, that express dataparallel computations on a high abstraction level. The goal of our high-level abstraction is to express computations agnostic from hardware and optimization details, and thus in a user-productive manner, while still capturing all information relevant for generating high-performance program code. The building blocks of our abstraction are based on the algebraic MDH formalism which is an approach toward formalizing data parallelism (we compare in detail to the existing work on MDHs in Section 6.6).

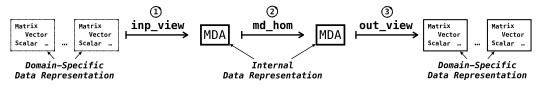

Figure 5 shows a basic overview of our high-level representation. We express data-parallel computations using exactly three higher-order functions only (a.k.a. *patterns* or *skeletons* [Gorlatch and Cole, 2011] in programming terminology): (1) inp\_view transforms the domain-specific input data (e.g., a matrix and a vector in the case of matrix-vector multiplication) to a **Multi-Dimensional Array (MDA)** which is our internal data representation and defined later in this section; (2) md\_hom expresses the data-parallel computation; (3) out\_view transforms the computed MDA back to the domain-specific data representation.

In the following, after informally discussing an introductory example in Section 2.1, we formally define and discuss each higher-order function in detail in Section 2.2 (function md\_hom) and Section 2.3 (functions inp\_view and out\_view). Sections 2.2 and 2.3 introduce and present the internals and formal details of our approach, which are not relevant for the end user of our system—the user only needs to operate on the abstraction level discussed in Section 2.1.

#### 2.1 Introductory Example

Figure 6 shows how our high-level representation is used for expressing the example of matrixvector multiplication MatVec<sup>4</sup> (Figure 1). Computation MatVec takes as input a matrix  $M \in T^{I \times K}$ and vector  $v \in T^K$  of arbitrary scalar type<sup>5</sup> T and sizes  $I \times K$  (matrix) and K (vector), for arbitrary but fixed positive natural numbers  $I, K \in \mathbb{N}$ .<sup>6</sup> In the figure, based on index function  $(i, k) \rightarrow (i, k)$ and  $(i, k) \rightarrow (k)$ , high-level function inp\_view computes a function that takes M and v as input and maps them to a two-dimensional array of size  $I \times K$  (referred to as *input MDA* in the following and defined formally in the next subsection). The MDA contains at each point (i, k) the pair  $(M_{i,k}, v_k) \in T \times T$  comprising element  $M_{i,k}$  within matrix M (first component) and element  $v_k$ within vector v (second component). The input MDA is then mapped via function md\_hom to an output MDA of size  $I \times 1$ , by applying multiplication \* to each pair  $(M_{i,k}, v_k)$  within the input

<sup>&</sup>lt;sup>4</sup>The expression in Figure 6 can also be extracted from straightforward, annotated sequential code [Rasch et al., 2020b,c]. <sup>5</sup>We consider as *scalar types* integers  $\mathbb{Z}$  (a.k.a. int in programming), floating point numbers  $\mathbb{Q}$  (a.k.a. float or double), any fixed collection of types (a.k.a. *record* or *struct*), and so on. We denote the set of scalar types as TYPE in the following.

<sup>&</sup>lt;sup>6</sup>We denote by  $\mathbb{N}$  the set of positive natural number  $\{1, 2, ...\}$ , and we use  $\mathbb{N}_0$  for the set of natural numbers including 0.

(De/Re)-Composition of Data-Parallel Computations via MDHs

Fig. 6. High-level expression for Matrix-Vector Multiplication (MatVec).<sup>7</sup>

MDA, and combining the obtained intermediate results within the MDA's first dimension via ++ (concatenation-also defined formally in the next subsection) and in second dimension via + (point-wise addition). Finally, function out\_view computes a function that straightforwardly maps the output MDA, of size  $I \times 1$ , to MatVec's result vector  $w \in T^{I}$ , which has scalar type T and is of size I. For the example of MatVec, the output view is trivial, but it can be used in other computations (such as matrix multiplication) to conveniently express more advanced variants of computations (e.g., computing the result matrix of matrix multiplication as transposed, as demonstrated later).<sup>7</sup>

#### 2.2 Function md\_hom

Higher-order function md\_hom is introduced by Rasch and Gorlatch [2016] to express MDH functions—a formal representation of data-parallel computations—in a convenient and structured way. In the following, we recapitulate the definition of MDHs and function md\_hom, but in a more general and formally more precise setting than done in the original MDH work.

To define MDH functions, we first need to introduce two central building blocks used in the definition of MDHs: (1) MDAs-the data type on which MDHs operate and which uniformly represent domain-specific input and output data (scalar, vectors, matrices, ...), and (2) combine operators which we use to combine elements within a particular dimension of an MDA.

#### **MDAs**

Definition 1 (MDA). An MDA **a** that has dimensionality  $D \in \mathbb{N}$ , size  $N \in \mathbb{N}^D$ , index sets  $I_1, \ldots, I_D \subset$  $\mathbb{N}_0$ , and scalar type  $T \in \mathsf{TYPE}$  is a function with the following signature:

$$\mathfrak{a}: I_1 \times \ldots \times I_D \to T$$

We refer to  $I_1 \times \ldots \times I_D \rightarrow T$  as the *type* of MDA **a**.

Notation 1. For better readability, we denote MDAs' types and accesses to them using a notation close to programming. We often write:

$-\mathfrak{a} \in T[I_1, \ldots, I_D]$  instead of  $\mathfrak{a} : I_1 \times \ldots \times I_D \rightarrow T$  to denote the type of MDA  $\mathfrak{a}$ ;  $-\mathfrak{a} \in T[N_1, \ldots, N_D]$  instead of  $\mathfrak{a} : [0, N_1)_{\mathbb{N}_0} \times \cdots \times [0, N_D)_{\mathbb{N}_0} \to T;^{8}$  $-\mathfrak{a}[i_1,\ldots,i_D]$  instead of  $a(i_1,\ldots,i_D)$  to access MDA  $\mathfrak{a}$  at position  $(i_1,\ldots,i_D)$ .

Figure 7 shows six MDAs for illustration. For example, the left part of the figure shows MDA a which is of type  $\mathfrak{a} : I_1 \times I_2 \to T$ , for  $I_1 = \{0, 1\}$ ,  $I_2 = \{0, 1, 2, 3\}$ , and  $T = \mathbb{Z}$  (integer numbers). Note that MDAs named  $\mathfrak{a}^{(1,1)}, \mathfrak{a}^{(1,2)}, \mathfrak{a}^{(2,1)}, \mathfrak{a}^{(2,2)}, \mathfrak{a}^{(2,3)}$  in Figure 7 can be considered as *parts* (a.k.a. *tiles* in programming) of MDA  $\mathfrak{a}$ : the MDA named  $\mathfrak{a}^{(1,1)}$  represents the first row of  $\mathfrak{a}$ , MDA  $\mathfrak{a}^{(2,2)}$  the third column of  $\mathfrak{a}$ , etc. We formally define and use *partitionings* of MDAs in Section 3.

<sup>&</sup>lt;sup>7</sup> Our technical implementation takes as input a representation that is equivalent to Figure 6, expressed via straightforward program code (see Rasch [2024], Section A.4). <sup>8</sup>We denote by  $[L, U]_{\mathbb{N}_0} := \{ n \in \mathbb{N}_0 \mid L \le n < U \}$  the half-open interval of natural numbers (including 0) between L (incl.)

and U (excl.).

A. Rasch

$$\mathfrak{a} = \underbrace{\begin{bmatrix} 1 & 2 & 3 & 4 \\ a[0,0] & a[0,1] & a[0,2] & a[0,3] \\ \vdots & \vdots & \vdots & \vdots \\ a[1,0] & a[1,1] & a[1,2] & a[1,3] \end{bmatrix}}_{eT[\ I_1:=\{0,1\},\ I_2:=\{0,1,2,3\}\]} \qquad \mathfrak{a}^{(1,1)} = \underbrace{\begin{bmatrix} 1 & 2 & 3 & 4 \\ a[0,0] & a[0,1] & a[0,2] & a[0,3] \\ \vdots & \vdots & \vdots & \vdots \\ a[1,0] & a[1,1] & a[1,2] & a[1,3] \end{bmatrix}}_{eT[\ I_1:=\{0,1\},\ I_2:=\{0,1,2,3\}\]} \qquad \mathfrak{a}^{(1,2)} = \underbrace{\begin{bmatrix} 5 & 6 & 7 & 8 \\ a[1,0] & a[1,1] & a[1,2] & a[1,3] \end{bmatrix}}_{eT[\ I_1^{(1,2)}:=\{1\},\ I_2^{(1,2)}:=\{0,1,2,3\}\]} \qquad \mathfrak{a}^{(2,2)} = \underbrace{\begin{bmatrix} 3 \\ a[0,0] \\ 7 \\ a[1,0] \end{bmatrix}}_{a[1,1]} \qquad \mathfrak{a}^{(2,3)} = \underbrace{\begin{bmatrix} 4 \\ a[0,3] \\ 8 \\ a[1,3] \end{bmatrix}}_{a[1,3]} \qquad \mathfrak{a}^{(2,3)} = \underbrace{\begin{bmatrix} 4 \\ a[0,3] \\ 8 \\ a[1,3] \end{bmatrix}}_{eT[\ I_1^{(2,1)}:=\{0,1\},\ I_2^{(2,1)}:=\{0,1\}\]} eT[\ I_1^{(2,2)}:=\{0,1\},\ I_2^{(2,2)}:=\{2\}\]} eT[\ I_1^{(2,3)}:=\{0,1\},\ I_2^{(2,3)}:=\{3\}\]$$

Fig. 7. MDA examples.

#### **Combine Operators**

A central building block in our definition of MDHs is a *combine operator*. Intuitively, we use a combine operator to combine all elements within a particular dimension of an MDA. For example, in Figure 1 (matrix-vector multiplication), we combine elements of the two-dimensional MDA via combine operator *concatenation* in MDA's first dimension and via operator *point-wise addition* in the second dimension. Technically, combine operators are functions that take as input two MDAs and yield a single MDA as their output.

We now define *combine operators* formally, and we illustrate this formal definition afterward using the example operators *concatenation* and *point-wise combination*.

*Definition 2 (Combine Operator).* We refer to any binary function  $\otimes$  of type

$$\circledast: T[I_1, \dots, P, \dots, I_D] \times T[I_1, \dots, Q, \dots, I_D] \to T[I_1, \dots, R, \dots, I_D]$$

as combine operator that has scalar type  $T \in TYPE$ , dimensionality  $D \in \mathbb{N}$ , and operating dimension  $d \in [1, D]_{\mathbb{N}}$ . We denote combine operator's type concisely as CO.

*Example 1 (Concatenation).* We define *concatenation* (in dimension d) as function  $+_d$  of type

$$+_{d}: T[I_{1}, \dots, P_{1}, \dots, I_{D}] \times T[I_{1}, \dots, Q_{1}, \dots, I_{D}] \rightarrow T[I_{1}, \dots, P \cup Q_{1}, \dots, I_{D}]$$

and that is computed as

The function is well defined when *P* and *Q* are disjoint. We usually use an infix notation for  $\#_d$ , i.e., we write  $\mathfrak{a}_1 \#_d \mathfrak{a}_2$  instead of  $\#_d(\mathfrak{a}_1, \mathfrak{a}_2)$ , and we refrain from  $\#_d$ 's subscript *d* when it is clear from the context.

(De/Re)-Composition of Data-Parallel Computations via MDHs

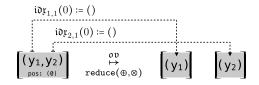

Fig. 8. MDH property illustrated on a two-dimensional example computation.

*Example 2 (Point-Wise Combination).* We define *point-wise combination* (in dimension *d*), according to a binary function  $\oplus$  :  $T \times T \rightarrow T$  (e.g., addition), as function  $\overrightarrow{\bullet}_d$  of type

$$\overrightarrow{\bullet}_{d}: \underbrace{T \times T \to T}_{\oplus} \to T[I_{1}, \dots, \{0\}, \dots, I_{D}] \times T[I_{1}, \dots, \{0\}, \dots, I_{D}] \to T[I_{1}, \dots, \{0\}, \dots, I_{D}]$$

point-wise combination (according to  $\oplus$  )

that is computed as

$$\overrightarrow{\bullet}_{d}(\oplus)(\mathfrak{a}_{1},\mathfrak{a}_{2})[i_{1},\ldots,0,\ldots,i_{D}] \coloneqq \mathfrak{a}_{1}[i_{1},\ldots,0,\ldots,i_{D}] \oplus \mathfrak{a}_{2}[i_{1},\ldots,0,\ldots,i_{D}]$$

The input MDAs are assumed to have index set  $\{0\}$  in the operating dimension d; otherwise,  $\overrightarrow{\bullet}(\oplus)$  is undefined. We refrain from  $\overrightarrow{\bullet}_d(\oplus)$ 's subscript d when it is clear from the context. For brevity, we often write  $\oplus$  only, instead of  $\overrightarrow{\bullet}_d(\oplus)$ , and we usually use an infix notation for  $\oplus$ .

#### **MDHs**

Now that we have defined MDAs (Definition 1) and combine operators (Definition 2), we can define *MDH functions*. Intuitively, a function *h* operating on MDAs is an MDH iff we can apply the function independently to parts of its input MDA and combine the obtained intermediate results to the final result using combine operators; this can be imagined as a typical divide-and-conquer pattern. Compared to classical approaches, e.g., *list homomorphisms* [Bird, 1989; COLE, 1995; Gorlatch, 1999], a major characteristic of MDH functions is that they allow (de/re)-composing computations in multiple dimensions (e.g., in Figure 1, in both the concatenation dimension as well as in the point-wise addition dimension), rather than being limited to a particular dimension only (e.g., only the concatenation dimension or only point-wise addition dimension, respectively). We will see later in this article that a multi-dimensional (de/re)-composition approach is essential to efficiently exploit the hardware of modern architectures which require fine-grained cache blocking and parallelization strategies to achieve their full performance potential.

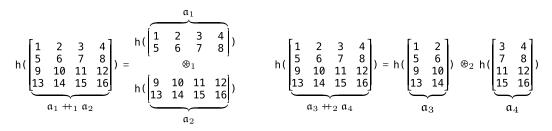

Figure 8 illustrates the MDH property informally on a simple, two-dimensional input MDA. In the left part of the figure, we split the input MDA in dimension 1 (i.e., horizontally) into two parts  $\mathfrak{a}_1$  and  $\mathfrak{a}_2$ , apply the MDH function h independently to each part, and combine the obtained intermediate results to the final result using the MDH function h's combine operator  $\mathfrak{B}_1$ . Similarly, in the right part of Figure 8, we split the input MDA in dimension 2 (i.e., vertically) into parts and combine the results via MDH function h's second combine operator  $\mathfrak{D}_2$ .

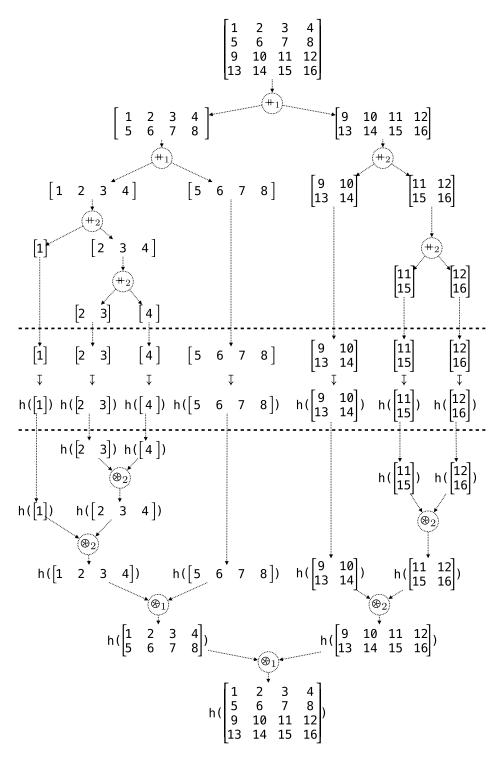

Figure 9 shows an artificial example in which we apply the MDH property (illustrated in Figure 8) recursively. We refer in Figure 9 to the part above the horizontal dashed lines as *de-composition phase* and to the part below dashed lines as *re-composition* phase.

Fig. 9. MDH property recursively applied to a two-dimensional example computation.

(De/Re)-Composition of Data-Parallel Computations via MDHs

Definition 3 (MDH). A function

$$h: T^{\text{INP}}[I_1, \ldots, I_D] \rightarrow T^{\text{OUT}}[J_1, \ldots, J_D]$$

is an *MDH* that has *input scalar type*  $T^{\text{INP}} \in \text{TYPE}$ , *output scalar type*  $T^{\text{OUT}} \in \text{TYPE}$ , and *dimensionality*  $D \in \mathbb{N}$ , iff for each  $d \in [1, D]_{\mathbb{N}}$ , there exists a combine operator  $\otimes_d$  (Definition 2), such that for any concatenated input MDA  $\mathfrak{a}_1 +_d \mathfrak{a}_2$  in dimension d, the *homomorphic property* is satisfied:

$$h(\mathfrak{a}_1 + \mathfrak{a}_2) = h(\mathfrak{a}_1) \otimes_d h(\mathfrak{a}_2)$$

We denote the type of MDHs concisely as MDH.

MDHs are defined such that applying them to a concatenated MDA in dimension d can be computed by applying the MDH h independently to the MDA's parts  $\mathfrak{a}_1$  and  $\mathfrak{a}_2$  and combining the intermediate results afterward by using its combine operator  $\otimes_d$ , as also informally discussed above.

*Example 3 (Function Mapping).* A simple example MDH is *function mapping* [González-Vélez and Leyton, 2010], computed by higher-order function  $map(f)(\mathfrak{a})$ , which applies a user-defined scalar function  $f: T^{INP} \to T^{OUT}$  to each element within a *D*-dimensional MDA  $\mathfrak{a}$ . Function map(f) is an MDH whose combine operators are concatenation # in all of its *D* dimensions (Example 1).

*Example 4 (Reduction).* A further MDH function is *reduction* [González-Vélez and Leyton, 2010], implemented as higher-order function  $red(\oplus)(\mathfrak{a})$ , which combines all elements within a *D*-dimensional MDA  $\mathfrak{a}$  using a user-defined binary function  $\oplus : T \times T \to T$ . Reduction's combine operators are point-wise combination  $\overrightarrow{\bullet}(\oplus)$  in all dimensions (Example 2).

We show how Examples 3 and 4 (and particularly also more advanced examples) are expressed in our high-level representation in Section 2.4, based on higher-order functions md\_hom, inp\_view, and out\_view (Figure 5) which we introduce in the following.

#### Higher-Order Function md\_hom

We define higher-order function md\_hom which conveniently expresses MDH functions in a uniform and structured manner. For this, we exploit that any MDH function is uniquely determined by its combine operators and its behavior on singleton MDAs, as informally illustrated in the following figure:

|                 |                                                                                                               |          |          |        |          |          |          | $\otimes_2$ |             |       |       |       | $\otimes_2$ |  |

|-----------------|---------------------------------------------------------------------------------------------------------------|----------|----------|--------|----------|----------|----------|-------------|-------------|-------|-------|-------|-------------|--|

| [1 2 3 4        | 41                                                                                                            | <b>1</b> | h([1])   | h([2]) | h([3])   | h([4])   |          | f(1)        | f(2)        | f(3)  | f(4)  |       |             |  |

| L 1             | $ \begin{bmatrix} 1 & 2 & 3 & 4 \\ 5 & 6 & 7 & 8 \\ 9 & 10 & 11 & 12 \\ 13 & 14 & 15 & 16 \end{bmatrix} ) = $ |          | h([5])   | h([6]) | h([7])   | h([8])   | _        | f(5)        | f(6)        | f(7)  | f(8)  |       |             |  |

| <sup>n</sup> (9 | 10                                                                                                            | 11<br>15 | $12^{+}$ | =      | h([9])   | h([10])  | h ([11]) | h ([12])    | =           | f(9)  | f(10) | f(11) | f(12)       |  |

| [12             | 14                                                                                                            | 12       | то]      |        | h ([13]) | h ([14]) | h ([15]) | h ([16])    | $\otimes_1$ | f(13) | f(14) | f(15) | f(16) €     |  |

Here, f is the function on scalar values that behaves the same as h when restricted to singleton MDAs:  $f(\mathfrak{a}[i_1, \ldots, i_D]) \coloneqq h(\mathfrak{a})$ , for any MDA  $\mathfrak{a} \in T[\{i_1\}, \ldots, \{i_D\}]$  consisting of only one element that is accessed by (arbitrary) indices  $i_1, \ldots, i_D \in \mathbb{N}_0$ . For singleton MDAs, we usually use f instead of h, because f can be defined more conveniently by the user as h (which needs to handle MDAs of arbitrary sizes, and not only singleton MDAs as f). Also, since f takes as input a scalar value (rather than a singleton MDA, as h), the type of f also becomes simpler, which further contributes to simplicity.

We now formally introduce function  $md_hom$  which uniformly expresses any MDH function, by using only the MDH's behavior f on scalar values and the MDH's combine operators.

Definition 4 (Higher-Order Function md\_hom). The higher-order function md\_hom is of type

$$\mathsf{md\_hom}: \underbrace{\mathsf{SF}}_{f} \times \underbrace{(\mathsf{CO} \times \ldots \times \mathsf{CO})}_{\circledast_1 \ldots, \circledast_D} \xrightarrow{\rightarrow_p} \underbrace{\mathsf{MDH}}_{\mathsf{md\_hom}(f, (\circledast_1, \ldots, \circledast_D))}$$

where SF denotes the set of scalar functions of type  $T^{\text{INP}} \to T^{\text{OUT}}$ . Function md\_hom is partial (indicated by  $\rightarrow_p$  instead of  $\rightarrow$ ), which we motivate after this definition. The function takes as input a scalar function f and a tuple of D-many combine operators  $(\otimes_1, \ldots, \otimes_D)$ , and it yields a function md\_hom $(f, (\otimes_1, \ldots, \otimes_D))$  which is defined as

$$\mathsf{md\_hom}(f, (\circledast_1, \ldots, \circledast_D))(\mathfrak{a}) \coloneqq \underset{i_1 \in I_1}{\circledast_1} \ldots \underset{i_D \in I_D}{\circledast_D} f(\mathfrak{a}[i_1, \ldots, i_D]).$$

The combine operators' underset notation denotes straightforward iteration.<sup>9</sup> For md\_hom, we require by definition the homomorphic property (Definition 3), i.e., for each  $d \in [1, D]_{\mathbb{N}}$ , it must hold:

$$\mathsf{md\_hom}(f, (\circledast_1, \dots, \circledast_D))(\mathfrak{a}_1 + _d \mathfrak{a}_2) = \\ \mathsf{md\_hom}(f, (\circledast_1, \dots, \circledast_D))(\mathfrak{a}_1) \otimes_d \mathsf{md\_hom}(f, (\circledast_1, \dots, \circledast_D))(\mathfrak{a}_2).$$

Using Definition 4, we express any MDH function uniformly via higher-order function md\_hom using only the MDH's behavior f on scalar values and its combine operators  $\otimes_1, \ldots, \otimes_D$ . The other direction also holds: each function expressed via md\_hom is an MDH function, because we require the homomorphic property for md\_hom.

Note that function md\_hom is defined as partial function, because the homomorphic property is not met for all potential combinations of combine operators, e.g.,  $\otimes_1 = +$  (point-wise addition) and  $\otimes_2 = *$  (point-wise multiplication). However, in many real-world examples, an MDH's combine operators are a mix of concatenations and point-wise combinations according to the same binary function. The following lemma proves that any instance of the md\_hom higher-order function for such a mix of combine operators is a well-defined MDH function.

LEMMA 1. Let  $\oplus$  :  $T \to T$  be an arbitrary but fixed associative and commutative binary function on scalar type  $T \in \text{TYPE}$ . Let further  $\otimes_1, \ldots, \otimes_D$  be combine operators of which any is either concatenation (Example 1) or point-wise combination according to binary function  $\oplus$  (Example 2). It holds that  $\text{md}_{\text{hom}}(f, (\otimes_1, \ldots, \otimes_D))$  is well defined.

PROOF. Proved by Rasch [2024], Section B.5.

MDH functions are defined (Definition 3) such that they uniformly operate on MDAs (Figure 5). We introduce higher-order function inp\_view to transform domain-specific inputs (e.g., a matrix and a vector in the case of matrix-vector multiplication) to an MDA, and we use function out\_view to transform the output MDA back to the domain-specific data requirements (like storing it as a transposed matrix in the case of matrix multiplication, or splitting it into multiple outputs as we will see later with examples). We introduce both higher-order functions in the following.

$<sup>^{9}</sup>$  We implicitly interpret the output scalar of function f as a singleton MDA, as combine operators operate on MDAs and not on scalars (formal details provided by Rasch [2024], Definition 4).

#### 2.3 View Functions

In the following, after introducing **Buffers (BUF)** which represent domain-specific input and output data in our approach (scalars, vectors, matrices, etc.), we define in Sections 2.3.1 and 2.3.2 the concepts of *input views* and *output views*—both are central building blocks in our approach. We define *input views* as arbitrary functions that map a collection of user-defined BUFs to our internal MDA data representation (Figure 5); higher-order function inp\_view is then introduced to conveniently compute an important class of input view functions that are relevant for expressing real-world computations. Correspondingly, Section 2.3.2 defines *output views* as functions that transform an MDA to a collection of BUFs, and higher-order function out\_view is introduced to conveniently compute important output views. Finally, we discuss in Section 2.3.3 the relationship between higher-order function inp\_view and out\_view: we prove that both functions are inversely related to each other, allowing arbitrarily switching between our internal MDA representation and our domain-specific BUF representation (as required for our code generation process discussed later).

Definition 5 (Buffer). A Buffer (BUF) b that has dimensionality  $D \in \mathbb{N}_0$ ,<sup>10</sup> size  $N \coloneqq \{N_1, \ldots, N_D\} \in \mathbb{N}^D$ , and scalar type  $T \in \mathsf{TYPE}$  is a function with the following signature:

$$\mathfrak{b}: [0, N_1)_{\mathbb{N}_0} \times \ldots \times [0, N_D)_{\mathbb{N}_0} \to T \cup \{\bot\}.$$

Here, we use  $\perp$  to denote the *undefined value*. We refer to  $[0, N_1)_{\mathbb{N}_0} \times \ldots \times [0, N_D)_{\mathbb{N}_0} \rightarrow T \cup \{\perp\}$  as the *type* of BUF b, which we also denote as  $T^{N_1 \times \ldots \times N_D}$ . Analogously to Notation 1, we write  $\mathfrak{b}[i_1, \ldots, i_D]$  instead of  $\mathfrak{b}(i_1, \ldots, i_D)$  to avoid a too heavy usage of parentheses.

In contrast to MDAs, a BUF always operates on a contiguous range of natural numbers starting from 0, and a BUF may contain undefined values. These two differences allow straightforwardly transforming BUFs to data structures provided by low-level programming languages (e.g., *C arrays*, as used in OpenMP, CUDA, and OpenCL).

Note that in our generated program code (discussed later in Section 3), we implement MDAs on top of BUFs, as straightforward aliases that access BUFs, so that we do not need to transform MDAs to low-level data structures and/or store them otherwise physically in memory.

2.3.1 Input Views. We define input views as any function that compute an MDA from a collection of (user-defined) BUFs. For example, in the case of MatVec, its input view takes as input two BUFs—a matrix and a vector—and it yields a two-dimensional MDA containing pairs of matrix and vector elements (illustrated in Figure 1). In contrast, the input view of Jacobi1D takes as input a single BUF (representing a vector) only, and it computes an MDA containing triples of BUF elements (Figure 2).

Definition 6 (Input View). An input view from *B*-many BUFs,  $B \in \mathbb{N}$ , of arbitrary but fixed types  $T_b^{N_1^b \times \ldots \times N_{D_b}^b}$ ,  $b \in [1, B]_{\mathbb{N}}$ , to an MDA of arbitrary but fixed type  $T[I_1, \ldots, I_D]$  is any function iv of type:

$$\mathfrak{iv}:\underbrace{\underbrace{\overset{B}{\underset{b=1}{\times}}T_{b}^{N_{1}^{b}\times\ldots\times N_{D_{b}}^{b}}}_{\text{BUFs}} \rightarrow_{p} \underbrace{T[I_{1},\ldots,I_{D}]}_{\text{MDA}}$$

We denote the type of *iv* as IV.

<sup>&</sup>lt;sup>10</sup>We use the case D = 0 to represent scalar values (details provided in Rasch [2024], Section B.7).

ACM Transactions on Programming Languages and Systems, Vol. 46, No. 3, Article 10. Publication date: October 2024.

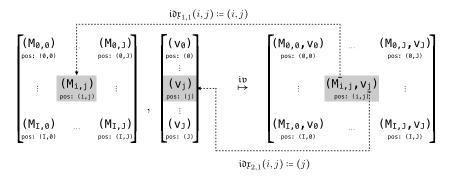

Fig. 10. Input view illustrated using the example MatVec.

*Example 5 (Input View*—MatVec). The input view of MatVec on a 1024 × 512 matrix and 512-sized vector (sizes chosen arbitrarily) is defined as

$$\underbrace{\left[\begin{array}{c}M(i,k)\end{array}\right]_{i\in[0,1024)_{\mathbb{N}_{0}},k\in[0,512)_{\mathbb{N}_{0}}}}_{\text{BUF (Matrix)}},\underbrace{\left[\begin{array}{c}v(k)\end{array}\right]_{k\in[0,512)_{\mathbb{N}_{0}}}}_{\text{BUF (Vector)}}\mapsto\underbrace{\left[\begin{array}{c}M(i,k),v(k)\end{array}\right]_{i\in[0,1024)_{\mathbb{N}_{0}},k\in[0,512)_{\mathbb{N}_{0}}}}_{\text{MDA}}$$

*Example 6 (Input View*—Jacobi1D). The input view of Jacobi1D on a 512-sized vector is defined as

$$\underbrace{\left[\begin{array}{c} v(i) \end{array}\right]_{i \in [0,512)_{\mathbb{N}_0}}}_{\text{BUF (Vector)}} \mapsto \underbrace{\left[\begin{array}{c} v(i+0), v(i+1), v(i+2) \end{array}\right]_{i \in [0,512-2)_{\mathbb{N}_0}}}_{\text{MDA}}.$$

In the following, we introduce higher-order function inp\_view which conveniently computes important input views from user-defined index functions  $\mathbf{idx}_{b,a} : \{0, 1, ...\} \rightarrow \{0, 1, ...\}, b \in [1, B]_{\mathbb{N}}, a \in [1, A_b]_{\mathbb{N}}$ , in a uniform, structured manner. Here,  $B \in \mathbb{N}$  represents the number of BUFs that the computed input view will take as input, and  $A_b$  represents the number of accesses to the *b*-th BUF required for computing an individual MDA element.

In the case of MatVec (Figure 1), we use B := 2 because MatVec has two input BUFs: a matrix M (the first input of MatVec and thus identified by b = 1) and a vector v (identified by b = 2). For the number of accesses, we use for the matrix  $A_1 := 1$ , as one element is accessed within matrix M to compute an individual MDA element—matrix element M[i, k] for computing MDA element at position (i, k). For the vector, we use  $A_2 := 1$ , as the single element v[k] is accessed within the vector. The index functions of MatVec are  $i\mathfrak{ds}_{1,1}(i, k) := (i, k)$  (used to access the matrix) and  $i\mathfrak{ds}_{2,1}(i, k) := (k)$  (used for the vector).

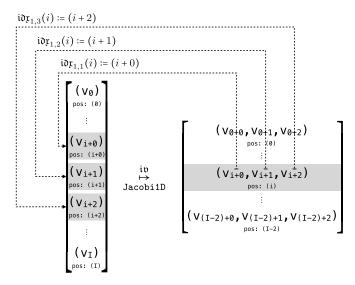

In contrast, for Jacobi1D (Figure 2), we use B := 1 because Jacobi1D has vector v as its only input, and we use  $A_1 := 3$  because the vector is accessed three times to compute an individual MDA element at arbitrary position i: first access v[i + 0], second access v[i + 1], and third access v[i + 2]. The index functions of Jacobi1D are  $idx_{1,1}(i) := (i + 0)$ ,  $idx_{1,2}(i) := (i + 1)$ , and  $idx_{1,3}(i) := (i + 2)$ .

Figures 10 and 11 use the examples MatVec and Jacobi1D to informally illustrate how function inp\_view uses index functions to compute input views. In the two figures, we use domain-specific identifiers for better clarity: in the case of MatVec, we use for its two input BUFs the identifiers M and v instead of  $b_1$  and  $b_2$ , as well as identifiers i and j instead of  $i_1$  and  $i_2$  for index variables; for Jacobi1D, we use identifier v instead of  $b_1$  and i instead of  $i_1$ .

Fig. 11. Input view illustrated using the example Jacobi1D.

$\label{eq:Index Functions: idx_{1,1},...,idx_{B,A_B}} and it is defined as$

$$\underbrace{(\mathbf{i}\mathfrak{d}\mathfrak{x}_{b,a})_{b\in[1,B]_{\mathbb{N}},a\in[1,A_{b}]_{\mathbb{N}}}}_{\text{Index Functions}} \mapsto \underbrace{(\underbrace{\mathfrak{b}_{1},\ldots,\mathfrak{b}_{B}}_{\text{BUFs}}) \stackrel{\text{iv}}{\mapsto} \underbrace{\mathfrak{a}}_{\text{MDA}}}_{\text{Input View}}$$

for

$$\mathfrak{a}[i_1,\ldots,i_D] \coloneqq (\mathfrak{a}_{b,a}[i_1,\ldots,i_D])_{b\in[1,B]_{\mathbb{N}},a\in[1,A_b]_{\mathbb{N}}}$$

and

$$\mathfrak{a}_{b,a}[i_1,\ldots,i_D] := \mathfrak{b}_b[\mathfrak{idx}_{b,a}(i_1,\ldots,i_D)]$$

Higher-order function inp\_view takes as input a collection of index functions of types IDX-FCT, and it computes an input view of type IV (Definition 6) based on the index functions, as illustrated in Figures 10 and 11.

Note that function inp\_view is not capable of computing every kind of input view function (Definition 6). For example, inp\_view cannot be used for computing MDAs that are required for expressing computations on sparse data formats [Hall, 2020], because such MDAs need dynamically accessing BUFs. This limitation of inp\_view can be relaxed by generalizing our index functions toward taking additional, dynamic input arguments, which we consider as future work (as outlined in Section 8).

A. Rasch

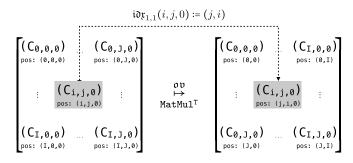

Fig. 12. Output view illustrated using the example transposed matrix multiplication.

*Notation 2 (Input Views).* For better readability, we use the following notation for the twodimensional structure of index functions taken as input by function inp\_view, inspired by Lattner et al. [2021]:

inp\_view(  $ID_1: idx_{1,1}, \ldots, idx_{1,A_1}, \ldots, ID_B: idx_{B,1}, \ldots, idx_{B,A_B}$  )

Here,  $ID_1, \ldots, ID_B$  denote arbitrary, user-defined identifiers (e.g.,  $ID_1 = "M"$  and  $ID_2 = "v"$  for MatVec).

Example 7. Function inp\_view is used for MatVec and Jacobi1D (in Notation 2) as follows:

$$\underbrace{\underline{MatVec:}}_{a=1} \qquad inp\_view(M: \underbrace{(i,k) \mapsto (i,k)}_{a=1}, v: \underbrace{(i,k) \mapsto (k)}_{a=1}) \\ \underbrace{\underline{Jacobi1D:}}_{a=1} \qquad inp\_view(v: \underbrace{(i) \mapsto (i+0)}_{a=1}, \underbrace{(i) \mapsto (i+1)}_{a=2}, \underbrace{(i) \mapsto (i+2)}_{a=3}) \\ \underbrace{\underline{Jacobi1D:}}_{b=1} \qquad \underbrace{Lacobined}_{b=1}$$

2.3.2 Output Views. An output view is the counterpart of an input view: in contrast to an input view which maps BUFs to an MDA, an output view maps an MDA to a collection of BUFs. In the following, we define output views, and we introduce higher-order function out\_view which computes output views in a structured manner (analogously to function inp\_view for input views).

Figures 12 and 13 illustrate output views informally using the examples *transposed Matrix Multiplication* and *Double Reduction*.

In the case of transposed matrix multiplication (Figure 12), the computed output MDA (the computation of matrix multiplication is presented later and not relevant for our following considerations) is stored via an output view as a matrix in a transposed fashion, using index function  $(i, j, 0) \mapsto (j, i)$ . Here, the MDA's third dimension (accessed via index 0) represents the so-called reduction dimension of matrix multiplication, and it contains only one element after the computation, as all elements in this dimension are combined via addition.

For double reduction (Figures 13), we combine the elements within the vector twice—once using operator  $\oplus$  (e.g.,  $\oplus = +$  addition) and once using operator  $\otimes$  (e.g.,  $\otimes = *$  multiplication). The final outcome of double reduction is a singleton MDA containing a pair of two elements that represent the combined vector elements (e.g., the elements' sum and product). We store this MDA via an output view as two individual scalar values, using index functions  $(0) \mapsto ()^{11}$  for both pair elements.

<sup>&</sup>lt;sup>11</sup>The empty braces denote accessing a scalar value (details provided by Rasch [2024], Section B.7).

ACM Transactions on Programming Languages and Systems, Vol. 46, No. 3, Article 10. Publication date: October 2024.

Fig. 13. Output view illustrated using the example double reduction.

Definition 8 (Output View). An output view from an MDA of arbitrary but fixed type  $T[I_1, ..., I_D]$  to *B*-many BUFs,  $B \in \mathbb{N}$ , of arbitrary but fixed types  $T_b^{N_1^b \times ... \times N_{D_b}^b}$ ,  $b \in [1, B]_{\mathbb{N}}$ , is any function  $\mathfrak{ov}$  of type:

$$\mathfrak{ov}: \underbrace{T[I_1, \dots, I_D]}_{\text{MDA}} \xrightarrow{\rightarrow_p} \underbrace{\overset{B}{\underset{b=1}{\times}} T_b^{N_1^b \times \dots \times N_{D_b}^b}}_{\text{BUFs}}$$

We denote the type of  $\mathfrak{ov}$  as OV.

*Example 8 (Output View*—MatVec). The output view of MatVec computing a 1024-sized vector (size is chosen arbitrarily), of integers  $\mathbb{Z}$ , is defined as

$$\underbrace{\left[\begin{array}{c}w(i)\right]_{i\in[0,1024)_{\mathbb{N}_{0}},k\in\{0\}}}_{\text{MDA}}\mapsto\underbrace{\left[\begin{array}{c}w(i)\right]_{i\in[0,1024)_{\mathbb{N}_{0}}}_{\text{BUF (Vector)}}\right]}_{\text{BUF (Vector)}}$$

*Example 9 (Output View*-Jacobi1D). The output view of Jacobi1D computing a (512 – 2)-sized vector is defined as

$$\underbrace{\left[\begin{array}{c}w(i)\right]_{i\in[0,512-2)_{\mathbb{N}_{0}},k\in\{0\}}}_{\text{MDA}}\mapsto\underbrace{\left[\begin{array}{c}w(i)\right]_{i\in[0,512-2)_{\mathbb{N}_{0}}}}_{\text{BUF (Vector)}}$$

We define higher-order function out\_view formally as follows.

Definition 9 (Higher-Order Function out\_view). Function out\_view is of type

$\mathsf{out\_view}: \underbrace{\overset{B}{\underset{b=1}{\times}} \overset{A_b}{\underset{a=1}{\times}}}_{\operatorname{Buffer} Access} \underbrace{\mathsf{IDX-FCT}}_{\operatorname{Index} \operatorname{Function:} i\mathfrak{d}\mathfrak{x}_{b,a}} \to \underbrace{\mathsf{OV}}_{\operatorname{Output} \operatorname{View:} \mathfrak{ov}}$

Index Functions:  $idx_{1,1},...,idx_{B,A_B}$

which differs from inp\_view's type only in mapping index functions to OV (Definition 8), rather than IV (Definition 6). Function out\_view is defined as

$$\underbrace{(\mathfrak{id}\mathfrak{x}_{b,a})_{b\in[1,B]_{\mathbb{N}},a\in[1,A_b]_{\mathbb{N}}}}_{\text{Index Functions}} \mapsto \underbrace{\mathfrak{a}}_{\text{MDA}} \stackrel{\mathfrak{ov}}{\mapsto} \underbrace{(\underbrace{\mathfrak{b}_{1},\ldots,\mathfrak{b}_{B}}_{\text{BUFs}})}_{\text{Output View}}$$

for

$$\mathfrak{b}_b[\mathfrak{idx}_{b,a}(i_1,\ldots,i_D)] \coloneqq \mathfrak{a}_{b,a}[i_1,\ldots,i_D]$$

and

$$(\mathfrak{a}_{b,a}[i_1,\ldots,i_D])_{b\in[1,B]_{\mathbb{N}},a\in[1,A_b]_{\mathbb{N}}} \coloneqq \mathfrak{a}[i_1,\ldots,i_D]$$

i.e.,  $\mathfrak{a}_{b,a}[i_1, \ldots, i_D]$  is the element at point  $i_1, \ldots, i_D$  within MDA  $\mathfrak{a}$  that belongs to the *a*-th access of the *b*-th BUF. We set  $\mathfrak{b}_b[j_1, \ldots, j_{D_b}] := \bot$  (symbol  $\bot$  denotes the undefined value) for all BUF indices which are not in the function range of the index functions.

Note that the computed output view  $\mathfrak{ov}$  is partial (indicated by  $\rightarrow_p$  in Definition 8), because for non-injective index functions, it must hold  $\mathfrak{idx}_{b,a}(i_1,\ldots,i_D) = \mathfrak{idx}_{b,a'}(i'_1,\ldots,i'_D) \Rightarrow \mathfrak{a}_{b,a}[i_1,\ldots,i_D] = \mathfrak{a}_{b,a'}[i'_1,\ldots,i'_D]$  which may not be satisfied for each potential input MDA of the computed view.

*Notation 3 (Output Views).* Analogously to Notation 2, we denote out\_view for a particular choice of index functions as

out\_view(  $ID_1: idx_{1,1}, \ldots, idx_{1,A_1}, \ldots, ID_B: idx_{B,1}, \ldots, idx_{B,A_B}$  )

Example 10. Function out\_view is used for MatVec and Jacobi1D (in Notation 3) as follows:

$$\underbrace{\underline{\mathsf{MatVec:}}}_{b=1} \quad \mathsf{out\_view}(\ w: \underbrace{(i,k) \mapsto (i)}_{a=1} \ ) \qquad \underbrace{\underline{\mathsf{Jacobi1D:}}}_{b=1} \quad \mathsf{out\_view}(\ w: \underbrace{(i) \mapsto (i)}_{a=1} \ ) \\ \underbrace{\underbrace{\mathsf{Jacobi1D:}}}_{b=1} \quad \mathsf{out\_view}(\ w: \underbrace{(i) \mapsto (i)}_{a=1} \ ) \\ \underbrace{\mathsf{Jacobi1D:}}_{b=1} \quad \mathsf{out\_view}(\ w: \underbrace{(i) \mapsto (i)}_{a=1} \ ) \\ \underbrace{\mathsf{Jacobi1D:}}_{b=1} \quad \mathsf{out\_view}(\ w: \underbrace{(i) \mapsto (i)}_{a=1} \ ) \\ \underbrace{\mathsf{Jacobi1D:}}_{b=1} \quad \mathsf{out\_view}(\ w: \underbrace{(i) \mapsto (i)}_{a=1} \ ) \\ \underbrace{\mathsf{MatVec:}}_{a=1} \quad \mathsf{MatVec:}_{a=1} \quad \mathsf{$$

2.3.3 Relation between View Functions. We use view functions to transform data from their domain-specific representation (represented in our formalism as BUFs, Definition 5) to our internal, MDA-based representation (via input views) and back (via output views), as also illustrated in Figure 5. In our implementation presented later, we aim to access data uniformly in the form of MDAs, thereby being independent of domain-specific data representations. However, we aim to store the data physically in the domain-specific format, as such format is usually the more efficient representation. For example, we aim to store the input data of MatVec in the domain-specific matrix and vector format, rather than as an MDA, because the input MDA of MatVec contains many redundancies—each vector element once per row of the input matrix (as illustrated in Figure 10).

The following lemma proves that functions inp\_view and out\_view are invertible and that they are each others inverses. Consequently, the lemma shows how we can arbitrarily switch between the domain-specific and our MDA-based representation, and consequently also that we can implicitly identify MDAs with the domain-specific data representation. For example, for computing MatVec, we will specify the computations via pattern md\_hom which operates on MDAs (see Figure 5), but we use the view functions in our implementation to implicitly forward the MDA accesses to the physically stored BUF representation.

LEMMA 2. Let

inp\_view(  $ID_1 : idx_{1,1}, \ldots, idx_{1,A_1}, \ldots, ID_B : idx_{B,1}, \ldots, idx_{B,A_B}$  )

and

out\_view(ID<sub>1</sub>:  $idx_{1,1}, \ldots, idx_{1,A_1}, \ldots, ID_B$ :  $idx_{B,1}, \ldots, idx_{B,A_B}$ )

be two arbitrary instances of functions inp\_view and out\_view (in Notations 2 and 3), both using the same index functions  $idx_{1,1}, \ldots, idx_{B,A_B}$ .

It holds (index functions omitted via ellipsis for brevity):

inp\_view(...) o out\_view(...) = out\_view(...) o inp\_view(...) = id

PROOF. Follows immediately from Definitions 7 and 9.

The following figure illustrates the lemma using as example the inverse of MatVec's input view (shown in Figure 10):

#### 2.4 Examples

Figure 14 shows how our high-level representation is used for expressing different kinds of popular data-parallel computations. For brevity, we state only the index functions, scalar function, and combine operators of the higher-order functions; an expression as in Figure 6 is then obtained by straightforwardly inserting these building blocks into the higher-order functions.

Subfigure 1. We show how our high-level representation is used for expressing linear algebra routines: (1) Dot (*Dot Product*); (2) MatVec (*Matrix-Vector Multiplication*); (3) MatMul (*Matrix Multiplication*); (4) MatMul<sup>T</sup> (*Transposed Matrix Multiplication*) which computes matrix multiplication on transposed input and output matrices; (5) bMatMul (*batched Matrix Multiplication*) where multiple matrix multiplications are computed using matrices of the same sizes.

We can observe from the subfigure that our high-level expressions for the routines naturally evolve from each other. For example, the md\_hom instance for MatVec differs from the md\_hom instance for Dot by only containing a further concatenation dimension + for its *i* dimension. We consider this close relation between the high-level expressions of MatVec and Dot in our approach as natural and favorable, as MatVec can be considered as computing multiple times Dot—one computation of Dot for each value of MatVec's *i* dimension. Similarly, the md\_hom instance for MatMul is very similar to the expression of MatVec, by containing the further concatenation dimension *j* for MatMul's *j* dimension. The same applies to bMatMul: its md\_hom instance is the expression of MatMul augmented with one further concatenation dimension.

Regarding MatMul<sup>T</sup>, the basic computation part of MatMul<sup>T</sup> and MatMul are the same, which is exactly reflected in our formalisms: both MatMul<sup>T</sup> and MatMul are expressed using exactly the same md\_hom instances. The differences between MatMul<sup>T</sup> and MatMul lies only in the data accesses transposed accesses in the case of MatMul<sup>T</sup> and non-transposed accesses in the case of MatMul. Data accesses are expressed in our formalism, in a structured way, via view functions (as discussed in Section 2.3): for example, for MatMul<sup>T</sup>, we use for its first input matrix A the index function  $(i, j, k) \mapsto (k, i)$  for transposed access, instead of using index function  $(i, j, k) \mapsto (i, k)$  as for MatMul's non-transposed accesses.

Note that all md\_hom instances in the subfigure are well defined according to Lemma 1.

*Subfigure 2.* We show how convolution-style stencil computations are expressed in our high-level representation: (1) Conv2D expresses a standard convolution that uses a two-dimensional sliding window [Podlozhnyuk, 2007]; (2) MCC expresses a so-called *Multi-Channel Convolution* [Dumoulin and Visin, 2018]—a generalization of Conv2D that is heavily used in the area of deep learning; (3) MCC\_Capsule is a recent generalization of MCC [Hinton et al., 2018] which attracted high attention due to its relevance for advanced deep learning neural networks [Barham and Isard, 2019].

While our  $md_hom$  instances for convolutions are quite similar to those of linear algebra routines (they all use multiplication \* as scalar function and a mix of concatenations + and point-wise

|                     |   |             |             |    |             |            | inp_                        | view                        | out_view                    |

|---------------------|---|-------------|-------------|----|-------------|------------|-----------------------------|-----------------------------|-----------------------------|

| md_hom              | f | $\otimes_1$ | $\otimes_2$ | ⊗3 | $\otimes_4$ | Views      | А                           | В                           | C                           |

| Dot                 | * | +           |             |    |             | Dot        | $(k) \mapsto (k)$           | $(k) \mapsto (k)$           | (k) → ()                    |

| MatVec              | * | #           | +           |    |             | MatVec     | $(i,k) \mapsto (i,k)$       | $(i,k) \mapsto (k)$         | (i,k) → (i)                 |

| MatMul              | * | ++          | ++          | +  |             | MatMul     | $(i,j,k) \mapsto (i,k)$     | $(i,j,k) \mapsto (k,j)$     | (i,j,k) → (i,j)             |

| MatMul <sup>T</sup> | * | #           | #           | +  |             | $MatMul^T$ | $(i,j,k) \mapsto (k,i)$     | $(i,j,k) \mapsto (j,k)$     | $(i,j,k) \mapsto (j,i)$     |

| bMatMul             | * | #           | #           | #  | +           | bMatMul    | $(b,i,j,k) \mapsto (b,i,k)$ | $(b,i,j,k) \mapsto (b,k,j)$ | $(b,i,j,k) \mapsto (b,i,j)$ |

| 1) | ) Linear | Algebra | Routines |

|----|----------|---------|----------|

|----|----------|---------|----------|

| md_hom      | f | $\otimes_1$ | $\otimes_2$ | $\otimes_3$ | $\otimes_4$ | $\otimes_5$ | $\otimes_6$ | \$97 | $\otimes_8$ | ⊗9 | $\otimes_{10}$ |

|-------------|---|-------------|-------------|-------------|-------------|-------------|-------------|------|-------------|----|----------------|

| Conv2D      | * | #           | #           | +           | +           |             |             |      |             |    |                |

| MCC         | * | #           | +           | +           | +           | +           | +           | +    |             |    |                |

| MCC_Capsule | * | ++          | +           | +           | +           | +           | +           | +    | ++          | #  | +              |

|             | inp_vi                                     | ew                                     | out_view                               |  |  |  |

|-------------|--------------------------------------------|----------------------------------------|----------------------------------------|--|--|--|

| Views       | I                                          | F                                      | 0                                      |  |  |  |

| Conv2D      | $(p,q,r,s) \mapsto (p+r,q+s)$              | $(p,q,r,s) \mapsto (r,s)$              | $(p,q,r,s) \mapsto (p,q)$              |  |  |  |

| MCC         | $(n,p,\ldots) \mapsto (n,p+r,q+s,c)$       | $(n,p,\ldots) \mapsto (k,r,s,c)$       | $(n,p,\ldots) \mapsto (n,p,q,k)$       |  |  |  |

| MCC_Capsule | $(n,p,\ldots) \mapsto (n,p+r,q+s,c,mi,mk)$ | $(n,p,\ldots) \mapsto (k,r,s,c,mk,mj)$ | $(n,p,\ldots) \mapsto (n,p,q,k,mi,mj)$ |  |  |  |

|         |   |             |         |    |       | inp_                             | out_view                         |                                     |  |

|---------|---|-------------|---------|----|-------|----------------------------------|----------------------------------|-------------------------------------|--|

| md_hom  | f | $\otimes_1$ | <br>\$6 | ⊗7 | Views | A                                | В                                | C                                   |  |

| CCSD(T) | * | #           | <br>++  | +  | I1    | $(a,\ldots,g) \mapsto (g,d,a,b)$ | $(a,\ldots,g) \mapsto (e,f,g,c)$ | $(a,\ldots,g) \mapsto (a,\ldots,f)$ |  |

|         |   |             |         |    | 12    | $(a,\ldots,g) \mapsto (g,d,a,c)$ | $(a,\ldots,g) \mapsto (e,f,g,b)$ | $(a,\ldots,g) \mapsto (a,\ldots,f)$ |  |

3) Quantum Chemistry

|          |                 |             |             |             |          | inp_view                                        | out_view                  |

|----------|-----------------|-------------|-------------|-------------|----------|-------------------------------------------------|---------------------------|

| md_hom   | f               | $\otimes_1$ | $\otimes_2$ | $\otimes_3$ | Views    | I                                               | 0                         |

| Jacobi1D | J <sub>1D</sub> | #           |             |             | Jacobi1D | (i1) $\mapsto$ (i1+0) , (i1) $\mapsto$ (i1+1) , | (i1) → (i1)               |

| Jacobi2D | J <sub>2D</sub> | #           | #           |             | Jacobi2D | $(i1,i2) \mapsto (i1+0,i2+1)$ ,                 | $(i1,i2) \mapsto (i1,i2)$ |

| Jacobi3D | J <sub>3D</sub> | #           | #           | #           | Jacobi3D | (i1,i2,i3) → (i1+0,i2+1,i3+1) ,                 | (i1,i2,i3) → (i1,i2,i3)   |

4) Jacobi Stencils

5) Probabilistic Record Linkage

|          |                    |             |             |          | inp_                | out_view            |                     |  |

|----------|--------------------|-------------|-------------|----------|---------------------|---------------------|---------------------|--|

| md_hom   | f                  | $\otimes_1$ | $\otimes_2$ | Views    | Elems               | Bins                | Out                 |  |

| Histo    | f <sub>Histo</sub> | +           | ++          | Histo    | $(e,b) \mapsto (e)$ | $(e,b) \mapsto (b)$ | (e,b) → (b)         |  |

| GenHisto | f                  | Ð           | #           | GenHisto | $(e,b) \mapsto (e)$ | $(e,b) \mapsto (b)$ | $(e,b) \mapsto (b)$ |  |

6) Histogram

|                           |                     |             |                           | inp_view  | out_v     | view     |

|---------------------------|---------------------|-------------|---------------------------|-----------|-----------|----------|

| md_hom                    | f                   | $\otimes_1$ | Views                     | I         | 01        | 02       |

| map(f)                    | f                   | #           | map(f)                    | (i) → (i) | (i) → (i) |          |

| $reduce(\oplus)$          | id                  | Ð           | $reduce(\oplus)$          | (i) → (i) | (i) → ()  |          |

| $reduce(\oplus, \otimes)$ | $(x) \mapsto (x,x)$ | (⊕,⊗)       | $reduce(\oplus, \otimes)$ | (i) → (i) | (i) → ()  | (i) → () |

7) Map/Reduce Patterns

8) Prefix Sum Computations

Fig. 14. Data-parallel computations expressed in our high-level representation.

ACM Transactions on Programming Languages and Systems, Vol. 46, No. 3, Article 10. Publication date: October 2024.

2) Convolution Stencils

additions + as combine operators), the index functions used for the view functions of convolutions are notably different from those used for linear algebra routines: the index functions of convolutions contain arithmetic expressions (e.g., p+r and q+s) and thus access neighboring elements in their input—a typical access pattern in stencil computations that requires special optimizations [Hagedorn et al., 2018]. Moreover, convolution-style computations are often high-dimensional (e.g., 10 dimensions in the case of MCC\_Capsule), whereas linear algebra routines usually rely on less dimensions. Our experiments in Section 5 confirm that respecting the data access patterns and the high dimensionality of convolutions in the optimization process (as in our approach, which we discuss later) often achieves significantly higher performance than using optimizations chosen toward linear algebra routines, as in vendor libraries provided by NVIDIA and Intel for convolutions [Li et al., 2016].

Subfigure 3. We show how quantum chemistry computation Coupled Cluster (CCSD(T)) [Kim et al., 2019] is expressed in our high-level representation. The computation of CCSD(T) notably differs from those of linear algebra routines and convolution-style stencils, by accessing its high-dimensional input data in sophisticated transposed fashions: for example, the view function of CCSD(T)'s *instance one* (denoted as I1 in the subfigure) uses indices a and b to access the last two dimensions of its A input tensor (rather than the first two dimensions of the tensor, as would be the case for non-transposed accesses). For brevity, the subfigure presents only two CCSD(T) instances—in our experiments in Section 5, we present experimental results for nine different real-world CCSD(T) instances.

Subfigures 4–6. The subfigures present computations whose scalar functions and combine operators are different from those used in Subfigures 1–3 (which are in Subfigures 1–3 straightforward multiplications \*, concatenation +, and point-wise additions + only). For example, Jacobi stencils (Subfigure 4) use as scalar function the Jacobi-specific computation  $J_{nD}$  [Cecilia et al., 2012], and *Probabilistic Record Linkage* (PRL) [Christen, 2012], which is heavily used in data mining to identify duplicate entries in a database, uses a PRL-specific both scalar function wght and combine operator max<sub>PRL</sub> (point-wise combination via the PRL-specific binary operator max<sub>PRL</sub>) [Rasch et al., 2019b]. Histograms, in their generalized version [Henriksen et al., 2020] (denoted as GenHisto in Subfigure 6), use an arbitrary, user-defined scalar function *f* and a user-defined associative and commutative combine operator  $\oplus$ ; the standard histogram variant Histo is then a particular instance of GenHist, for  $\oplus = +$  (point-wise addition) and  $f = f_{Histo}$ , where  $f_{Histo}(e, b) = 1$  iff e = b and  $f_{Histo}(e, b) = 0$ otherwise.

Subfigure 7. We show how typical map and reduce patterns [González-Vélez and Leyton, 2010] are implemented in our high-level representation. Examples map(f) and reduce( $\oplus$ ) (discussed in Examples 3 and 4) are simple and thus straightforwardly expressed in our representation. In contrast, example reduce( $\oplus$ ,  $\otimes$ ) is more complex and shows how reduce( $\oplus$ ) is extended to combine the input vector simultaneously twice—once combining vector elements via operator  $\oplus$  and once using operator  $\otimes$ . The outcome of reduce( $\oplus$ ,  $\otimes$ ) are two scalars—one representing the result of combination via  $\oplus$  and the other of combination via  $\otimes$ —which we map via the output view to output elements  $O_1$  (result of  $\oplus$ ) and  $O_2$  (result of  $\otimes$ ), correspondingly; this is also illustrated in Figure 13.

Subfigure 8. We present prefix-sum computations [Blelloch, 1990] which differ from the computations in Subfigures 1–7 in terms of their combine operators: the operator used for expressing computations in Subfigure 8 is different from concatenation (Example 1) and point-wise combinations (Example 2). Computation scan( $\oplus$ ) uses as combine operator  $\#_{prefix-sum}(\oplus)$  which computes prefix-sum [Gorlatch and Lengauer, 1997] (formally defined by Rasch [2024], Section B.9) according to binary operator  $\oplus$ , and Maximum Bottom Box Sum (MBBS) [Farzan and Nicolet, 2019] uses a particular instance of prefix-sum for  $\oplus = +$  (addition).

#### 3 Low-Level Representation for Data-Parallel Computations

We introduce our low-level representation for expressing data-parallel computations. In contrast to our high-level representation, our low-level representation explicitly expresses the de-composition and re-composition of computations (informally illustrated in Figure 3). Moreover, our low-level representation is designed such that it can be straightforwardly transformed to executable program code, because it explicitly captures and expresses the optimizations for the memory and core hierarchy of the target architecture.

In the following, after briefly discussing an introductory example in Section 3.1, we introduce in Section 3.2 our formal representation of computer systems, which we refer to as *Abstract System Model (ASM)*. Based on this model, we define *low-level MDAs, low-level BUFs*, and *low-level combine operators* in Section 3.3, which are basic building blocks of our low-level representation.

Note that all details and concepts discussed in this section are not exposed to the end users of our system and therefore transparent for them: expressions in our low-level representation are generated fully automatically for the user, from expressions in our high-level representation (Figure 4), according to the methodologies presented later in Section 4 and auto-tuning [Rasch et al., 2021].

#### 3.1 Introductory Example

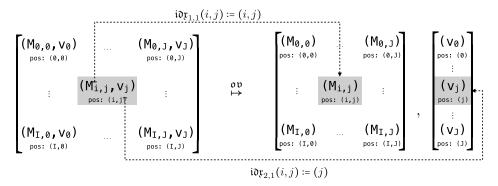

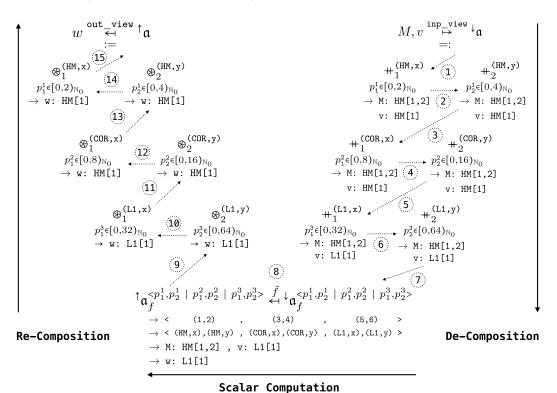

Figure 15 illustrates our low-level representation by showing how MatVec (Matrix-Vector Multiplication) is expressed in our representation. In our example, we use an input matrix  $M \in T^{512\times4096}$  of size 512 × 4096 (size chosen arbitrarily) that has an arbitrary but fixed scalar type  $T \in TYPE$ ; the input vector  $v \in T^{4096}$  is of size 4096, correspondingly.

For better illustration, we consider for this introductory example a straightforward, artificial target architecture that has only two memory layers—*Host Memory* (HM) and *Cache Memory* (L1)—and one *Core Layer* (COR) only; our examples presented and discussed later in this section target real-world architectures (e.g., CUDA-capable NVIDIA GPUs). The particular values of tuning parameters (discussed in detail later in this section), such as the number of threads and the order of combine operators, are chosen by hand for this example and as straightforward for simplicity.

Our low-level representations work in three phases: (1) *de-composition* (steps 1–7, in the right part of Figure 15), (2) *scalar* (step 8, bottom part of the figure), (3) *re-composition* (steps 9–15, left part). Steps are arranged from right to left, inspired by the application order of function composition.

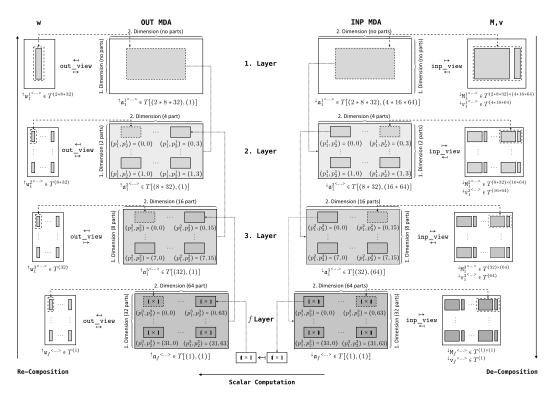

(1) De-Composition Phase. The de-composition phase (steps 1–7 in Figure 15) partitions input MDA  $\downarrow \mathfrak{a}$  (in the top right of Figure 15) to the structure  $\downarrow \mathfrak{a}_{f}^{<...>}$  (bottom right) which we refer to as *low-level MDA* and define formally in the next subsection. The low-level MDA represents a partitioning of MDA  $\downarrow \mathfrak{a}$  (a.k.a *hierarchical, multi-dimensional tiling* in programming), where each particular choice of indices  $p_1^1 \in [0,2)_{\mathbb{N}_0}$ ,  $p_2^1 \in [0,4)_{\mathbb{N}_0}$ ,  $p_1^2 \in [0,8)_{\mathbb{N}_0}$ ,  $p_2^2 \in [0,16)_{\mathbb{N}_0}$ ,  $p_1^3 \in [0,32)_{\mathbb{N}_0}$ ,  $p_2^3 \in [0,64)_{\mathbb{N}_0}$  refers to an MDA that represents an individual part of MDA  $\downarrow \mathfrak{a}$  (a.k.a. *tile* in programming—informally illustrated in Figure 7). The partitions are arranged on multiple layers (indicated by the *p*'s superscripts) and in multiple dimensions (indicated by subscripts)—as illustrated in Figure 16—according to the memory/COR of the target architecture and dimensions of the MDH computation: we partition for each of the target architecture's three layers (HM, L1, COR) and in each of the two dimensions of the MDH (dimensions 1 and 2, as we use example MatVec in Figure 15, which represents a two-dimensional MDH computation). Consequently, our partitioning approach allows efficiently exploiting each particular layer of the target architecture (both memory and core layers), and also optimizing for both dimensions of the target computation (in the case of MatVec, the *i*-dimension and also the *k*-dimension—see Figure 1), allowing fine-grained optimizations.

evel expression for straightforwardly computing Matrix-Vector Multiplication

Fig. 15. Low-level expression for straightforwardly computing Matrix-Vector Multiplication (MatVec) on a simple, artificial architecture with two memory layers (HM L1) and one COR. Dotted lines indicate data flow.